سرور اچ پی با رم DDR4

تغييرات عمدهاي در دنياي اينترفيس حافظه پيش روي ما قرار گرفتهاند و توجه به برنامههاي شركتهايي مانند AMD و Nvidia براي اتخاذ يك استاندارد حافظه با پهناي باند بالاتر، باعث شده تا اكنون زمان مناسبي براي صحبت درباره سه استاندارد جديد يعني Wide I/O، HBM و HMC باشد. اجازه بدهيد اين صحبت را با يك سوال ابتدايي آغاز كنيم: اساسا چرا به استانداردهاي رم جديد نياز داريم؟

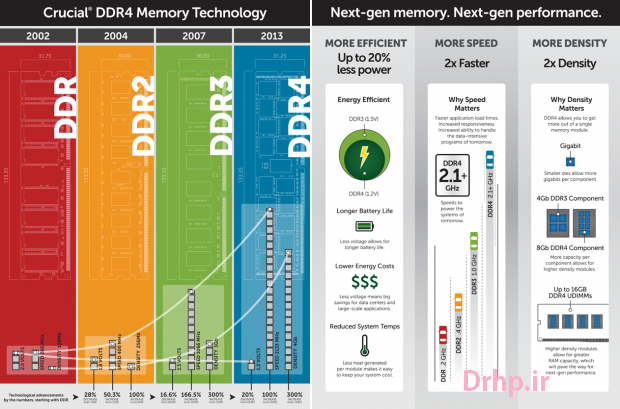

DDR4 و LPDDR4 هر دو بهسازيهاي افزايشي براي طراحيهاي DRAM موجود محسوب ميشوند. همانطور كه در ادامه خواهيد ديد، هر دو استاندارد مذكور مصرف برق و عملكرد را نسبت به استانداردهاي DDR3 و LPDDR3 بهبود ميبخشند اما جهشهاي بزرگي بهسمت جلو محسوب نميشوند. بسياري از فناوريهاي زيربنايي كه در اين استاندارد پشتيباني شدهاند، يك دهه يا حتي بيشتر از آن عمر دارند، يعني ريشه آنها به زماني برميگردد كه كل پهناي باند سيستم كسري از سطوح امروزي آن بود و پردازندههاي اصلي تنها به يك هسته پردازشي مجهز بودند.

در حالي كه استانداردها از آن زمان تا امروز بهطور قابل توجهي تكامل يافته، اما نبايد فراموش كنيم كه اولين SDRAM DIMM مدرن كار خود را روي يك اينترفيس 66 مگاهرتزي آغاز نمود و پهناي باندي معادل 533 مگابايت بر ثانيه را فراهم ميكرد. در مقابل، DDR4-3200 با فركانس 1600 مگاهرتز كار ميكند و پهناي باند آن به 25.6 گيگابايت بر ثانيه ميرسد. اين يك افزايش 48 برابري نسبت به 20 سال پيش محسوب ميشود، اما در عين حال به معناي آن است كه توانستهايم استاندارد را در يك مسير طولاني جلو ببريم. در حالي كه بحثهاي زيادي در مورد درستي تعريف يك استاندارد DDR5 سنتي وجود دارد، اما كل صنعت در اين زمينه به توافق نظر رسيدهاند كه يك راهكار جديد در اين زمينه، الزامي است.

خرید رم سرور hp

Wide I/O سامسونگ: پهناي باند فوقالعاده كم مصرف

Wide I/O و Wide I/O 2 توسط شركتهايي مانند سامسونگ پشتيباني ميشوند و طراحي شدهاند تا حداكثر پهناي باند ممكن را در پايينترين سطح مصرف برق ممكن براي SoCهاي موبايل فراهم نمايند. اين فناوري بيش از همه براي شركتهايي جذابيت دارد كه در زمينه توليد تلفنهاي هوشمند يا سيستمهاي مجتمع فعاليت ميكنند، حوزههايي كه نمايشگرهايي با تفكيكپذيري بالا فشار سنگيني را بر پهناي باند وارد ميكنند و از سوي ديگر ملزومات مصرف برق پايين نيز براي حفظ عمر باتري سيستم حياتي هستند.

Wide I/O بهطور اختصاصي براي پشتهسازي روي SoCها طراحي شده و براي به حداقل رساندن تداخل الكتريكي و همچنين مساحت اشغال شده توسط die، از اتصالات عمودي استفاده ميكند. اين وضعيت باعث بهبود اندازه بستهبندي ميشود اما در عين حال محدوديتهاي حرارتي خاصي را نيز بههمراه خواهد داشت زيرا حرارت منتشر شده از SoC بايد از كل die حافظه عبور كند. فركانسهاي كاري در اين استاندارد پايين هستند اما تعداد فراوان پايههاي I/O پهناي باند را با استفاده از يك گذرگاه حافظه كه 1024 بيت پهنا دارد، افزايش ميدهد.

Wide I/O اولين نسخه از اين استاندارد بود اما پيشبيني ميشود كه Wide I/O 2 عملا به بازار انبوه راه پيدا كند. با اينحال بحثهايي در اين زمينه وجود دارد كه انطباق واقعي با استاندارد مورد بحث تا عرضه Wide I/O 3 روي نخواهد داد. Wide I/O 3 سرانجام يك فاصله مهم را بين اين استاندارد و LPDDR4 ايجاد خواهد كرد. استاندارد Wide I/O توسط JEDEC تاييد شده است اما غالبا به سامسونگ نسبت داده ميشود زيرا اين شركت تلاش زيادي را براي رساندن آن به بازار انجام ميدهد. زمانبندي ورود Wide I/O به بازار مشخص نيست اما بعيد است كه حداقل در نيمه اول سال 2015 ابزارهاي مهمي با استاندارد مذكور معرفي شوند. از سوي ديگر احتمالا در نيمه دوم سال نيز شاهد گزينههاي محدودي در بين محصولات خود سامسونگ خواهيم بود.

Wide I/O آشكارا طراحي شده است تا يك اينترفيس 3 بعدي باشد، اما طراحيهاي 2.5 بعدي ميانجي از آن نيز امكانپذير هستند. از آنجايي كه بزرگترين چالش يك ساختار 3D Wide I/O خنك كردن پردازنده زير DRAM است، احتمالا اولين تراشهها مبتني بر طراحيهاي ميانجي 2.5 بعدي خواهند بود.

اينتل و ميكرون: Hybrid Memory Cube

در سوي ديگر ميدان، ما مكعب حافظه پيوندي را داريم كه يك استاندارد مشترك بين اينتل و ميكرون است. HMC طراحي شده تا بر حجم انبوه پهناي باند در سطح بالاتري از مصرف برق و هزينه نسبت به Wide I/O 2 تاكيد نمايد. اينتل و ميكرون مدعي هستند كه پهناي باندي معادل 400 گيگابايت بر ثانيه از طريق HMC امكانپذير خواهد بود. پيشبيني ميشود توليد HMC در سال 2016 آغاز شده و در سال 2017 بهطور تجاري قابل دسترسي باشد.

HMC يك استاندارد JEDEC نيست اما شركتهاي متعددي در توسعه آن همكاري ميكنند كه در ميان آنها ميتوان به اينتل، ميكرون، سامسونگ، مايكروسافت، ARM، Altera، HP و Xilinx اشاره كرد. يكي از اهداف عمده HMC، حذف مدار منطقي كنترل مضاعف از DIMMهاي مدرن، سادهسازي طراحي، اتصال كل پشته در يك پيكربندي 3 بعدي و سپس استفاده از يك لايه مدار منطقي كنترل واحد براي اداره كل ترافيك نوشتن/خواندن است.

HMC يك معماري را نويد ميدهد كه صراحتا براي پاسخ به سناريوهاي چند هستهاي و تحويل دادهها با پهناي باند بسيار بيشتر و تاخير كلي كمتر طراحي شده است. HMC فوقالعاده آيندهنگرانه است و تعداد زيادي از مشكلات مربوط به رايانش در مقياس انبوه را برطرف ميسازد اما در عين حال به چند پيشرفت عميق در توليد نيمههاديها وابسته است. در عين حال HMC گرانترين استاندارد جديد محسوب ميشود و تنها استانداردي است كه توسط JEDEC تاييد نشده است.

| مقايسه مصرف برق استانداردهاي مختلف |

تصوير فوق در سال 2011 منتشر شد اما نماي كلي آن هنوز دقيق است. در يك مقياس عظيم، مصرف برق حافظه در رم DDR3 و DDR4 رم بسيار بالاتر از آن است كه مقياسدهي كارآمد را فراهم سازد. كاهش مصرف برق به ميزان دو سوم ميتواند تاثير چشمگيري بر ابررايانش در چارچوب زماني 2020 داشته باشد.

AMD، Nvidia و Hynix: رم با پهناي باند بالا

در نهايت نوبت به High Bandwidth Memory ميرسد كه شركتهاي Hynix، AMD و Nvidia روي آن كار ميكنند. HBM صراحتا براي كاربردهاي گرافيكي طراحي شده است اما يك كاربرد اختصاصي از Wide I/O 2 محسوب ميشود. هر دو شركت AMD و Nvidia اين استاندارد را براي نسل بعدي GPUهاي خود اتخاذ كردهاند. در واقع Nvidia اعلام كرده كه در سال 2016 از اين استاندارد براي Pascal استفاده خواهد نمود. از سوي ديگر AMD نيز روي اين فناوري كار ميكند اما هنوز مشخص نكرده كه چه زماني پردازندههاي گرافيكي اين شركت از HBM پشتيباني خواهند كرد.

HBM از كانالهايي با پهناي 128 بيت استفاده ميكند و ميتواند تا 8 عدد از آنها را براي دستيابي به يك اينترفيس 1024 بيتي، پشتهسازي نمايد. كل پهناي باند در دامنه 128 تا 256 گيگابايت بر ثانيه است كه از پشتهسازي 4 تا 8 DRAM die بهدست ميآيد. هر كنترلر حافظه بهطور مستقل زمانبندي و كنترل ميشود. GPUهاي آينده كه با HBM ساخته ميشوند ميتوانند به پهناي باندي معادل 512 گيگابايت بر ثانيه تا يك ترابايت بر ثانيه براي حافظه برسند (در مقايسه با 336 گيگابايت بر ثانيه روي Black Titan امروزي.

تا جايي كه به هزينه و پهناي باند مربوط ميشود، HBM يك گزينه مياني بهشمار ميآيد. اين استاندارد بهاندازه Wide I/O ارزان نيست و بازدهي انرژي مشابهي را فراهم نميكند، اما بهطور صريح براي محيطهاي GPU با عملكرد بالا طراحي شده و هنوز بايد ارزانتر از HMC باشد.

همچنين بر حسب برنامه زمانبندي خود سامسونگ براي عرضه Wide I/O، ميتوان پيشبيني كرد كه HBM احتمالا اولين فناوري خواهد بود كه به بازار انبوه ميرسد.

همه گزينهها در كنار هم

در نهايت اجازه بدهيد ويژگيها و قابليتهاي اين استانداردها را در كنار يكديگر بررسي كنيم. پيش از هر چيز يك جدول جامع از هر سه استاندارد حافظه مورد بحث در اين مقاله بههمراه DDR4 و LPDDR4 را ببينيد.تصوير بعدي، هر سه راهكار را بر اساس پهناي باند، بازدهي انرژي و هزينه كلي در كنار استانداردهاي DDR4 و LPDDR4 نشان ميدهد.در سمت چپ، شما مصرف انرژي و پهناي باند را مشاهده ميكنيد در حالي كه تصوير سمت راست قيمت و پهناي باند را نشان ميدهد. آنچه كه تصاوير فوق در كنار يكديگر بيان ميكنند اين است كه DDR متعارف فاقد بازدهي انرژي مناسب بوده اما قيمت خوبي دارد. از سوي ديگر، استانداردهاي جديدي مانند Wide IO2 پهناي باند و سطح مصرف برق فوقالعادهاي را ارايه ميكنند، اما هزينه بالاتري دارند. HBM و HCM پهناي باند و مصرف برق را افزايش ميدهند، اما در عين حال قيمت بالاتري نيز دارند كه نشان ميدهد چرا اساسا براي كاربردهاي گرافيكي و انترپرايز در نظر گرفته شدهاند نه سختافزارهاي عمومي و موبايل.

در نهايت خطسير TSMC را براي معرفي هر يك از فناوريهاي جديد مشاهده ميكنيد. عرضه HBM از سال جاري آغاز خواهد شد، در حالي كه HMC براي سال 2016 برنامهريزي شده و Wide I/O تا 2016 يا 2017 در انتظار خواهد ماند. در اين مورد خاص ممكن است سامسونگ Wide I/O 2 را پيش از TSMC روانه بازار كند.

HP G11

HP G11 قیمت سرور HP Gen 10 | مشخصات و خرید سرور اچ پی g10

قیمت سرور HP Gen 10 | مشخصات و خرید سرور اچ پی g10 خرید سرور hp g9 | قیمت سرور اچ پی G9

خرید سرور hp g9 | قیمت سرور اچ پی G9 HP G8

HP G8